Troja Today

Angriffsziel Hardware

Beitrag von Dr.-Ing. Horst Gieser, Leiter CS Analyse & Test Fraunhofer EMFT, Einrichtung für Mikrosysteme und Festkörpertechnologien München

Hätten die Trojaner seinerzeit auf die Warnungen der Königstochter Kassandra gehört und das riesige Holzpferd – ein vermeintliches Weihgeschenk der Griechen – nicht in ihre Stadt geholt, wären sie wohl unbesiegt geblieben. Doch die Geschichte ging bekanntlich anders aus. Parallelen zu Troja finden sich im Zusammenhang mit Hardware-Trojanern. Über Datenschutz und Sicherheit im gesamten System.

Akzeptanz komplexer Informations- und Kommunikationssysteme

Ähnlich wie im alten Troja macht die Freude am technischen Fortschritt und seinen Möglichkeiten oft blind für die verborgenen Risiken. Vor allem die Integrität und der Schutz von Daten haben eine ebenso hohe gesellschaftliche wie wirtschaftliche Bedeutung. Moderne komplexe Informations- und Kommunikationssysteme in Anwendungsgebieten wie Internet of Things (IoT), Industrie 4.0, Health, autonomes Fahren oder kritische Infrastrukturen bieten unschätzbar viele Möglichkeiten – doch wirklich akzeptieren werden Nutzerinnen und Nutzer solche Systeme nur, wenn diese wirklich sicher vor unbefugtem Zugriff sind.

Schutz gegen Angreifer

Nur der kombinierte verifizierte Schutz auf Soft-, Firm- und Hardwareebene über die gesamte Lieferkette kann den Aufwand für Angriffe von Datendieben und Manipulatoren erhöhen und Risiken minimieren.

Hardwareseitig kann er nur durch den Einsatz von Sicherheitskomponenten mit hardwarebasierter Verschlüsselung erreicht werden. Diese können integraler Bestandteil von

- Systemen auf dem Chip (SOC – System on a Chip),

- als eigenständiger Chip im selben Gehäuse (SIP – System in a Package)

- oder als zusätzlicher Baustein (TPM – Trusted Platform Module) in einem System sein.

Sicherheit im gesamten Prozess

Die höchsten Sicherheitsanforderungen werden dabei an Bausteine gestellt, die in Reisedokumente und Bankkarten integriert werden. Auch wenn diese noch in etwas älteren Technologien in Europa hergestellt werden, haben die Kosten für Entwicklung und Massenherstellung von Bausteinen mit Strukturen von aktuell weniger als 10 nm die Fertigung von Europa zunehmend zu wenigen Auftragsfertigern (Foundry, Assembly, Test) vorwiegend nach Fernost verlagert. Diese sind Grundlage für die vorgenannten Anwendungen. Für europäische Nutzer gilt es, in der gesamten Wertschöpfungskette von den Entwurfsdaten bis hin zum fertigen Baustein oder gefertigten System Gefährdungen durch Angriffe, Manipulation und Fälschungen an der Quelle vorzubeugen.

Bei den zunehmend komplexen Bausteinen und Systemen ist keine vollständige Abdeckung durch elektrische Tests möglich. In manchen Fällen wird die Testbarkeit sogar bewusst eingeschränkt, um die Sicherheit zu erhöhen.

Analysiert und Verifikation sicherheitskritischer Teile

Vor diesem Hintergrund müssen exemplarisch zumindest die sicherheitskritischen Teile von gefertigten Bausteinen physisch analysiert und verifiziert werden können. Dies kann am wirksamsten durch Vergleich mit bekannten Entwurfsdaten erfolgen. Dieser Analyse- und Verifikationsprozess umfasst, wie von Lippmann et al. [1] gezeigt, grundsätzlich folgende Schritte:

- Analyse und Entfernung des Gehäuses in welchem sich auch mehrere integrierte Schaltungen neben- oder übereinander befinden können

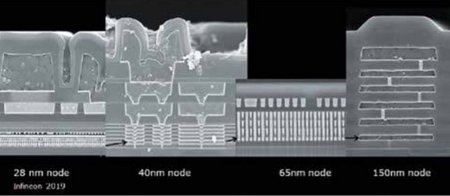

- Selektiver, planparalleler Abtrag der einzelnen Isolationsschichten und Freistellen der Metallisierungsebenen oder aktiven Ebenen auch bei gewölbten Bausteinen

- Abscannen der Strukturen mittels eines speziellen Rasterelektronenmikroskops mit einer Auflösung von wenigen Nanometer

- Erzeugung globaler Bilder (z. B. Metallisierungsebenen) aus den einzelnen Bildern (Stitching)

Zusätzliche Schritte

Bei vorhandenen Entwurfsdaten kann hier bereits der Vergleich mit den Analysedaten erfolgen. Bei unbekannten Bausteinen schließen sich die folgenden Stufen an:

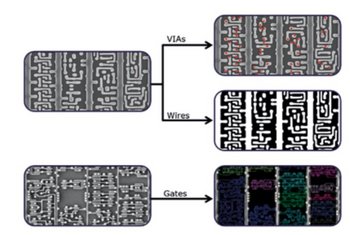

5. Erkennung und Differenzierung von Strukturen (Leiterbahnen, Vias, Transistoren)

und Zellen

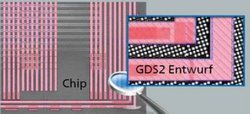

6. Vergleich mit Entwurfsdaten im GDS2-Format

7. Passgenaue Überlagerung dieser Ebenen und vertikalen Verbindungen

8. Erkennung von Schaltungsblöcken und Erzeugung eines Schaltplans

9. Analysen auf höherer Abstraktionsebene

Herausforderungen im Analyse- und Verifikationsprozess

Die Schlüsselherausforderungen dieses Prozesses, die insbesondere für die aktuellen Technologien zum Teil noch gelöst werden müssen, sind:

- Bei der Rückpräparation von 40 nm Technologien müssen für Chipgrößen bis über 100 mm² hinweg Toleranzen von wenigen 10 nm eingehalten werden.

- Die über mehrere Tage hinweg stabile Präzision und hohe Effizienz der Erzeugung von Bildern mit höchster Auflösung

- Die effiziente Verarbeitung der bei der Analyse entstehenden riesigen, mit Präparationsartefakten und Rauschen behafteten Datenmengen

- Vertikal integrierte Multi Chip Module

Projekte zur Weiterentwicklung der Prozesse

Die sich daraus ergebenden interdisziplinären Aufgaben und die Weiterentwicklung der Werkzeuge und Programme können nur in enger Zusammenarbeit eines Konsortiums mit den unterschiedlichen Schwerpunkten und Ressourcen sowie öffentlicher Förderung ganzheitlich bearbeitet werden.

Im Rahmen des durch das Bundesministerium für Bildung und Forschung BMBF geförderten Investitionsprojektes FMD werden auch hochwertige Geräte für das Sicherheitslabor der Fraunhofer EMFT, das noch 2019 nach CC-EAL6 zertifiziert werden soll, beschafft. Die Methoden werden seit 2017 auch im Rahmen der von BMBF geförderten Forschungsprojekte SyPASS und RESEC angewandt und weiterentwickelt. Zudem ist die Fraunhofer EMFT koordinierende Partnerin des vom Freistaat Bayern und der Fraunhofer-Gesellschaft geförderten Münchner Leistungszentrums »Sichere intelligente Systeme«.

Fazit

Auch wenn aktuell die Realisierung und Entdeckbarkeit von integrierten Hardware-Trojanern in der wissenschaftlichen Literatur akademischen Charakter besitzt und noch keine Fälle öffentlich bekannt geworden sind, sollten wir nicht vergessen: die grundsätzliche technische Möglichkeit dazu besteht und so könnte aus der Theorie schneller Praxis werden als gedacht. Solide Risikoanalysen in den verschiedenen kritischen Bereichen sollten daher eine realistische Bewertung der technischen Möglichkeiten, des Aufwands für Manipulationen sowie die Verfügbarkeit von Methoden zu deren Erkennung in integrierten Schaltungen beinhalten.

Quellen

[1] Bernhard Lippmann, Michael Werner, Niklas Unverricht, Aayush Singla, Peter Egger, Anja Dübotzky, Horst Gieser, Martin Rasche, Oliver Kellermann, Helmut Graeb, 2019. Integrated Flow for Reverse Engineering of Nanoscale Technologies. In Proceedings of the 24th Asia and South Pacific Design Automation Conference (ASPDAC‚ 19). ACM, New York, NY, USA, pp. 82-89.

Alle Abb. aus: [1] Integrated Flow for Reverse Engineering (...). Bilder reproduziert mit Genehmigung der Assoc. for Computing Machinery, NY, USA, 2019.

Erstmals erschienen in: TiB Ausgabe 2019 November/Dezember