Elektronik im Huckepack

MEMS/IC-System Produktion mittels 3D- und Panel-Integration

Beitrag von Dr. Peter Ramm und Josef Weber, Fraunhofer-Einrichtung für Mikrosysteme und Festkörper-Technologien EMFT, Rolf Aschenbrenner und Dr. Michael Töpper, Fraunhofer Institut für Zuverlässigkeit und Mikrointegration IZM

Um mit der rasanten Entwicklung im digitalen Zeitalter mithalten zu können, müssen die eingesetzten mikroelektronischen Systeme immer leistungsfähiger und multifunktionaler werden – und das bei niedrigsten Produktionskosten. Auch die Verbindungen zwischen den Bauelementen müssen daher höchste Anforderungen hinsichtlich Integrationsdichte und Zuverlässigkeit erfüllen. Die beiden innovativen Produktionsmethoden – Panel- und 3D-Integration – gelten als Schlüssel, um dies zukünftig zu erreichen. Mehr über die Methoden.

Hochleistungsfähige Chips und Leiterplatten

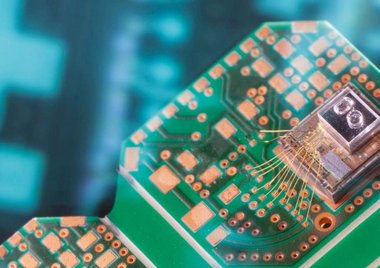

Integrierte Schaltungen (ICs) und Mikro-Elektro-Mechanische Systeme (MEMS) sind das Herzstück unzähliger Produkte, die unseren Alltag prägen – vom Smartphone über Fahrerassistenzsysteme bis hin zum Smart Home. Die Chips verfügen heute über so komplexe Funktionalitäten, dass sie eigentlich schon als Mini-Computer bezeichnet werden könnten: Ultra-miniaturisierte elektronische „Gehirne“ die auch mit Sensorik ausgestattet sind.

Möglich macht das insbesondere eine hochleistungsfähige 3D-Integration, bei der die Einzelkomponenten vertikal gestapelt und mit elektrischen Durchkontaktierungen und Chip-Verbindungen zu einem höchstintegrierten mikroelektronischem System verbunden werden. Mittels der 3D-Integration werden seit einigen Jahren Bild-Sensoren und Speicher-ICs der Spitzenklasse produziert.

Doch das alleine genügt nicht: Auch die Leiterplatte als Träger der aktiven und passiven Bauelemente muss an die steigenden Anforderungen angepasst werden. War der Umstieg von der Durchsteckmontage auf die Oberflächenmontagetechnik (SMD, Surface-mounted device) notwendig, um die steigende Anzahl an elektrischen Kontakten zu beherrschen, ist es nun Zeit für den nächsten Technologiesprung auf die Embedding Technologie: Nur so lässt sich die Miniaturisierung weiter vorantreiben, ohne die Leistungsfähigkeit des Gesamtsystems zu beeinträchtigen.

Wafer-Bonding – die Herausforderung bei der 3D-Integration

Der Trend zum Internet of Things (IoT) macht die 3D-Integration zu einer Schlüsseltechnologie, bringt aber auch Herausforderungen mit sich. Die oft heterogenen Komponenten eines Chips werden über einander gestapelt und mit elektrischen Durchkontaktierungen zu einem in drei Dimensionen integrierten System verbunden – mittels sog. „Wafer-Bonding“ (Through Silicon Vias, TSV).

Die gängigen Verfahren hierfür sind aber entweder in der Prozessführung kompliziert, was die Fertigungskosten hochtreibt, oder sie benötigen hohe Bondtemperaturen, was sich negativ auf Lebensdauer und Zuverlässigkeit der Bauteile auswirkt.

SLID Bonden: Niedertemperaturprozesse schonen die Bauteile

An der Fraunhofer EMFT in München wurde das sogenannte SLID Bonden (Solid-Liquid-Interdiffusion) entwickelt – in enger Kooperation mit Forschern von Infineon Technologies.

Dabei werden vertikale Kontakte mit einer niedrigschmelzenden Lotschicht zwischen zwei hochschmelzenden Metallen bei vergleichsweise niedrigen Temperaturen prozessiert, wobei die Bauelemente sowohl mechanisch als auch elektrisch verbunden werden. Die entsprechende Standardtechnologie im Münchener Institut nutzt dafür eine solide intermetallische Verbindung mit einem Schmelzpunkt von über 600 °C, die jedoch bei weit niedrigeren Temperaturen von unter 270 °C hergestellt wird. Dies garantiert hohe mechanische Robustheit der 3D-integrierten Bauelemente.

In patentierten Verfahren wurde die SLID Technik geeignet mit dem TSV Konzept kombiniert und zu einer höchst leistungsfähigen und kostengünstigen 3D-TSV Technologie weiterentwickelt. Es können hiermit Integrationsdichten von Millionen Kontakten pro Quadratzentimeter Fläche erreicht werden.

In Zusammenarbeit mit den Partnern Infineon, Sensonor und SINTEF wurde mit diesem 3D-Integrationsverfahren ein miniaturisierter drahtlos kommunizierender Reifendrucksensor hergestellt.

Das Internet der Dinge treibt die Entwicklung vorwärts

Der große Wettbewerbsdruck in IoT-Anwendungen verlangt jedoch zusätzlich nach immer kleineren, aber gleichzeitig leistungsfähigeren und robusten Systemen.

Um diesen Anforderungen gerecht zu werden, unterzeichnete die Fraunhofer EMFT im September 2016 eine Lizenzvereinbarung mit der XPERI Corp. und integrierte mit ZiBond® (Direct Oxide Bonding) und DBI® (Direct Bond Interconnect) zwei der modernsten 3D-Integrationstechnologien in ihr Leistungsportfolio. Beide Prozesse können bei vergleichsweise niedrigen Temperaturen von ca. 200 °C durchgeführt werden, was sich positiv auf Zuverlässigkeit und Lebensdauer der Bauelemente auswirkt.

Bei der DBI®-Technologie werden die Bauteile nach einer speziellen Vorbehandlung der verwendeten Kupfer- und Oxidoberflächen sowohl mechanisch als auch elektrisch verbunden. Da somit die aufwändige Prozedur des Durchkontaktierens entfällt, können die Systeme kostengünstig gefertigt werden – eine Grundvoraussetzungen für den Zugang zu Massenmärkten wie der Consumerelektronik. Ein weiterer Vorteil: Die „Pitches“ (Strukturbreite und Abstand) zwischen den Verbindungen betragen im günstigsten Fall nur noch 2 µm. Dies ermöglicht höchstintegrierte Chips mit enormer Leistungsfähigkeit.

Ein Forschungsziel für die nächsten Jahre steht für die Münchner Wissenschaftler auch schon fest: Hochleistungsfähige, miniaturisierte MEMS/IC Systeme mit Kommunikationsschnittstellen zur Vernetzung der smarten Produkte der Zukunft mit gigantischen Übertragungsraten.

Panel Level Packaging

Hersteller von Smartphones und ähnlichem kaufen die meisten Komponenten wie Speicherchips oder Mikro-Prozessoren von externen Herstellern. Ändern nun Zulieferer die Baugrößen ihrer Komponenten, muss die Leiterplatte als Träger neu konzipiert werden. Eine Möglichkeit, dies zu vermeiden, ist aktuell das Fan-out Wafer Level Packaging-Verfahren:

Hierfür werden die einzelnen Chips auf einen temporären Träger bestückt und über ein Mold-Verfahren zu einem neuen, rekonfigurierten Wafer zusammengefügt. Im Rahmen dieser Technik wird der Wafer, auf dem die ICs sitzen, vereinzelt und die geprüften Chips oder passiven Bauteile werden auf eine Folie platziert und anschließend mit einem hochgefüllten Epoxidharz umspritzt. Nach dem Ablösen des gemoldeten Wafers mit den eingebetteten Chips vom Träger kann nun eine Umverdrahtung aufgebracht und mehrere Chips miteinander verbunden werden. Allerdings begrenzt die maximale Größe des rekonfigurierten Wafers von derzeit 300 mm die Anzahl der Komponenten, die gleichzeitig darauf bearbeitet werden können.

Eine neue Technologie soll diese Grenze nun einreißen: Statt runder Waferformate werden rechteckige Substrate im Bereich von 610 x 457 mm² genutzt – damit können nun weitaus mehr Bauteile gleichzeitig in eine neue Form gebracht werden. Ein Wechsel von der Wafer- zur Panel Level-Technologie bringt also ein vielfach höheres Produktionsvolumen. Besonders den Bereich der Consumer-Electronics mit seinen Tablets und Smartphones wird die neue Technologie nachhaltig prägen und sich damit für diese Art von Packaging einen Markt erschließen, dessen Wert auf 170 Millionen USD geschätzt wird (Yole 2016).

Literatur

- R. Beica, J.-C. Eloy and P. Ramm: „Key Applications and Market Trends for 3D Integration and Interposer Technologies“. Handbook of 3D Integration, Vol. 3, WileyVCH (2014).

- M. Töpper: „Wafer Level Chip Size Packaging“ in Materials for Advanced Packaging, Hrsg.: D. Lu, C.P. Wong, 2nd Edition, Springer 2016.

Erstmals erschienen in: TiB Ausgabe 2017 September/Oktober